娱乐圈爆料王玉雯是谁啊?亲爱的读者们,今天我要给大家揭秘一个娱乐圈的神秘人物——王玉雯。她是谁?为何会成为娱乐圈的爆料王?让我们一起揭开这个谜团吧!一、王玉雯是谁?王玉雯,一个听起来普通的名字,却隐藏着不为人知的秘密。她是一...

-

娱乐新闻

娱乐新闻

娱乐圈爆料王玉雯是谁啊,揭秘神秘艺人身份

-

娱乐新闻

娱乐新闻

人教社社长爆料案例最新,最新爆料案例背后的教育行业真相

你知道吗?最近人教社社长可是爆出了一个大瓜,让人瞠目结舌!这不,我就迫不及待地来和你分享一下这个新鲜出炉的案例,保证让你大呼过瘾!一、揭秘人教社社长爆料背后的故事那天,阳光明媚,人教社社长在一场教育论坛上突然抛出了一个重磅炸...

-

娱乐新闻

娱乐新闻

三国杀貂蝉爆料视频大全,揭秘绝世美女的传奇人生与武将风采

你知道吗?最近在互联网上掀起了一股三国杀貂蝉的热潮,各种爆料视频层出不穷,简直让人眼花缭乱。今天,我就要带你一起走进这个精彩的世界,看看那些让人心跳加速的貂蝉爆料视频大全!一、貂蝉的美丽传说说起貂蝉,那可是中国古代四大美女之...

-

娱乐新闻

娱乐新闻

成龙吃瓜爆料视频大全,吃瓜爆料视频大全大汇总

你知道吗?最近娱乐圈可是热闹非凡,尤其是成龙大哥,竟然亲自下场吃瓜,还拍成了视频,这可真是让人大呼过瘾啊!今天,就让我带你一起看看成龙吃瓜爆料视频大全,看看这位功夫巨星是如何化身“吃瓜群众”的!成龙大哥的吃瓜日常成龙大哥可是...

-

娱乐新闻

娱乐新闻

吉林爆料直播事件最新,揭秘背后真相与网络舆论风暴

最近网上可是炸开了锅,咱们吉林的一件直播事件成了大家茶余饭后的热门话题。这不,我就迫不及待地来给你揭秘一下这场风波的来龙去脉,让你一探究竟!直播风波初现端倪话说那天,吉林的一位名叫小王的年轻人,突发奇想,决定在抖音上开个直播...

-

娱乐新闻

娱乐新闻

盐城女学生爆料视频播放,揭开校园暴力真相

最近网上可是炸开了锅,一条关于盐城女学生的爆料视频在网络上疯狂传播。这事儿可真是让人摸不着头脑,咱们一起来探究探究,看看这背后到底隐藏着怎样的秘密。一、视频内容揭秘首先,让我们来一睹为快,看看这个视频到底讲了些什么。据网友爆...

-

网红明星

网红明星

娱乐吃瓜茶小猫,揭秘茶小猫的幕后故事

你知道吗?最近娱乐圈可是热闹非凡,吃瓜群众们纷纷拿出小本本,记录下每一个细节。这不,今天咱们就来聊聊那些让人捧腹大笑的娱乐吃瓜事件,还有那些可爱的小猫,它们可是成了不少网友的新宠哦!娱乐吃瓜,笑料百出首先,咱们得说说那些让人...

-

最新爆料

最新爆料

河北唐县爆料新闻视频大全,聚焦民生热点,展现社会百态

最近河北唐县可是热闹非凡呢!各种爆料新闻视频层出不穷,让人看得眼花缭乱。今天,就让我带你一起走进这个充满故事的小县城,看看那些让人津津乐道的视频吧!一、神秘事件引关注话说有一天,唐县某地突然出现了一个神秘事件。一位网友在社交...

-

娱乐头条

娱乐头条

霍德被爆料视频大全最新,揭秘爆料视频背后的真相与争议

最近网上可是炸开了锅,大家都在热议一个话题——霍德被爆料视频大全!没错,就是那个曾经红极一时的明星,这次可是被拍了个正着。下面,就让我带你一探究竟,看看这个视频大全里都有些啥?一、视频内容揭秘首先,咱们得弄清楚这个视频大全里...

-

网红明星

网红明星

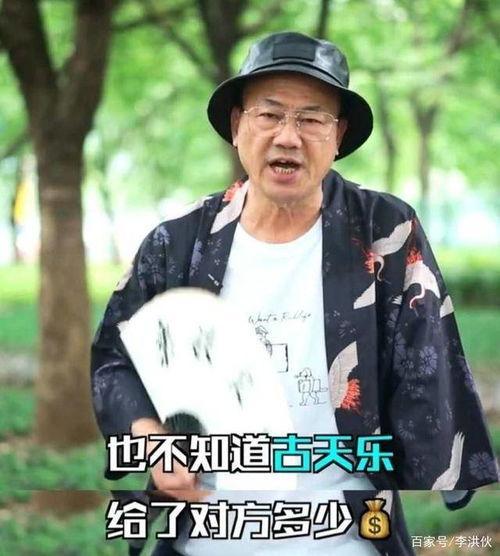

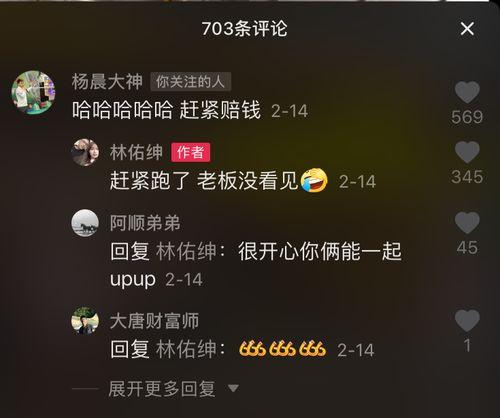

杨晨大神爆料羽毛球视频,羽毛球高手实战技巧全解析

最近在羽毛球圈里可是炸开了锅呢!杨晨大神竟然亲自爆料了一段羽毛球教学视频,这可是羽毛球爱好者们的福音啊!快来跟我一起看看,这位羽毛球界的传奇人物到底有哪些独门秘籍吧!一、杨晨大神的羽毛球之路提起杨晨,那可是羽毛球界的传奇人物...